eTeak: A High-Level Synthesis Framework for Implementing Mixed Sync-Async Architectures

"Computer Science is not just about coding to get a job done,

it's also about broader thinking skills like computational thinking

and abstraction and modeling and design."

Simon Peyton Jones

What's eTeak

eTeak is a high-level synthesis EDA, that aims to generate Globally Asynchronous Locally Synchronous (GALS) SoCs from a timing-free description. eTeak is a synchronous extension to the Teak Synthesis system which is a dataflow backend for the Balsa language. eTeak adopts Synchronous Elastic Protocol to provide a common timing behaviour in the computation and communication domains. This work is a part of The GAELS project supported by EPSRC under research grant EP/I038306/1. eTeak is still under development and is currently maintained by eTeak Group at the University of Manchester.

Why reinventing the wheel?

Despite the fact that there are many High-Level Synthesis tools developed in academia and industry, just a handful of them provide the source code for the researchers including LegUP and Chisel (which has been rebranded from a HLS tool to a HDL flow suitable for constructing large-scale hardware). eTeak is the first open-source framework that exploits asynchronous synthesis techniques to realise fine-grained synchronous circuits capable of running at different clock frequencies.

Visual engine (xTeak) for Parallel Programming:

Allows experienced users to perform rapid application development and non-technical users to extend their application. It is also very useful to monitor the concurrent events in the design and could be used as a very powerful mechanism for debugging purpose. It is impossible to think of a parallel archiecture without a decent monitoring scheme for test and debug as we human being think sequentially, perform tasks in order and are inhabit of squeezing tasks into the sequential timed slots. The new paradigm of parallel programming and design is very beyond this scope and a proper monitoring mechanism could be very useful indeed.eTeak towards IoT Modeling and Multiple-FPGA Synthesis:

Hardware/Software Co-design of large-scale systems permits prompt realisation of Big ideas. With this enhanced productivity provided for the designers in the community through a distributed dataflow synthesis infrastructure, design, simulation, integration, evaluation and verification of large-scale ideas such as IoT will be possible in near future.Software

Feel free to fork eTeak synthesiser from here: https://github.com/balangs/eTeak and contribute to it today!

*eTeak Installation Guide for ghc>6:

The modules such as Array, Monad, etc could not be compiled with ghc version later than 6. They should be specifically defined with their associated libraries: Data.Array, control.Monad...Ghc compiler with version later than 7.4.1 has compatibility issue with compiling bits.hs therefore ghc 7.4.1 needs to be considered.

Pre-requirements: libgmp-dev , libgmp3-dev , zlib1g-dev

Note: libgmp.so.10 library should be linked to libgmp.so.10 library with ln -s command

Installing ghc and cabal:

1- Download and Install ghc 7.4.1 from source (www.haskell.org/ghc/dist/7.4.1/ (filename due to architecture) )

- Note:After installing, the ghc installation path should be linked to ghc via ln -s.

- Note:The ghc installation path should be added to PATH environment variable.

2- Download and Install cabal 1.18.1.6 from source (www.haskell.org/cabal/release/cabal-1.18.1.6/Cabal-1.18.1.6.tar.gz )

- Note: build cabal with ghc like below:

ghc --make Setup.hs

./Setup configure --user

./Setup build

./Setup install

- Note: Before installing cabal, remove old packages if they exist.

3- Download and Install cabal-install version 1.18.1.0 from source (https://www.haskell.org/cabal/release/cabal-install-1.18.1.0/ cabal-install-1.18.1.0.tar.gz)

- Note: Add cabal to path environment variable

Adding gtk and gtk2hs build tools:

4- Install the following libraries:

- Libglib2.0-dev, libcairo2.0-dev, libpango1.0-dev, libgtk2.0-dev, libglade2.0-dev

5- Install alex and happy packages with cabal install.

6- Install glade with cabal install

- Note:glade will install all the packages for gtk2hs itself. The version is 0.12.1 which is ok.

- Note: By installing gtk2hs-buildtools and gtk with cabal install separately, Theversion would be 0.13 which is not compatible with eTeak.

Synchronous Elastic Dataflows of eTeak:

Couple of notes around the novel synchronous elastic dataflows of eTeak that needs attention: 1- A set of files associated with the SELF protocol such as ectrl.v, SRLOR_H.v, SRLOR_L.v, etc. need to be included in your project. eTeak doesn't generate them automatically so you have to include them in your project for simulation purpose. Download SELF zip file (320K) 2- In a synchronous elastic design there is a clock and reset signal (see every top-level design modules) hence the clock frequency needs to be set to an appropriate value based on the critical path. The frequency of the clock in current examples is defined in top.v testbench file.3- Buffering matters! one can simply buffer every link in the design and achieve a very fast (frequency) design. But remember that over buffering kills throughput in a synchronous design (it's not always true with the asynchronous systems). Please see the paper #4 where this phenomena is explained.

4- A high-level description of a dataflow system is consist of one or more loops. To get your design work a single buffer in every loop can guarantee deadlock-freedom (see paper #4). This rule is little bit different in the asynchronous domian where three buffers are needed for every loop in the design to guarantee deadlock-freedom.

Publications

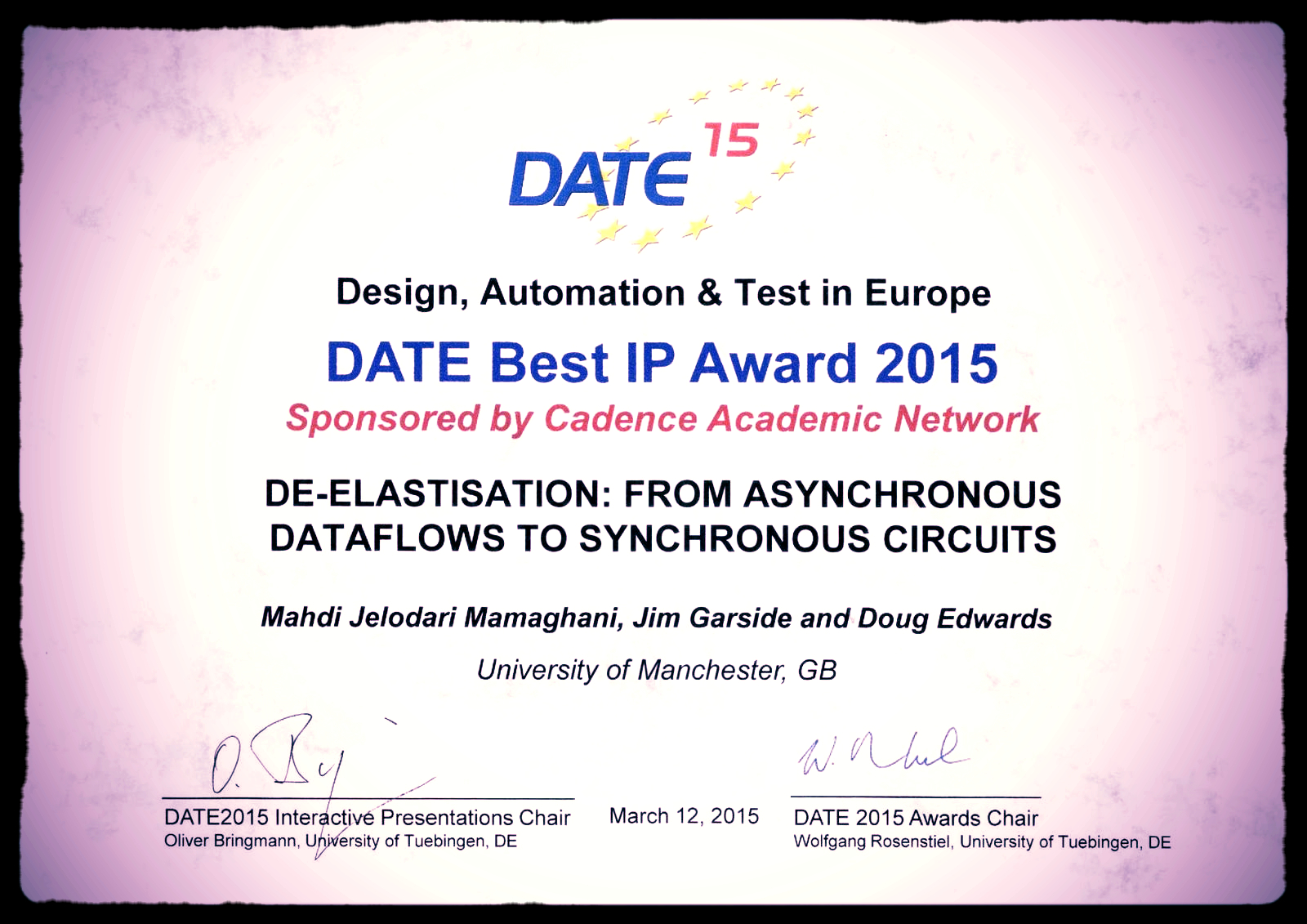

5. Mahdi Jelodari Mamaghani, Jim Garside, Doug Edwards, "De-Elastisation: From Asynchronous Dataflows to Synchronous Circuits," in Proc. of IEEE/ACM conference on Design Automation and Test in Europe (DATE), March 2015, France. Download PDF (757K) [DATE Best IP Award Winner] 4. Mahdi Jelodari Mamaghani, Jim Garside, Will Toms, Doug Edwards, "Optimised Synthesis of Asynchronous Elastic Dataflows by Leveraging Clocked EDA," The Euromicro Conference on Digital System Design (DSD), August 2014, Verona, Italy. Download PDF (1046K) 3. Mahdi Jelodari Mamaghani, Will Toms, Andrew Bardsley, Jim Garside, "Exploiting Synchrony for Area and Performance Improvement in the Asynchronous Domain," Intl. Symposium on Asynchronous Circuits and Systems (ASYNC), May 2014, Potsdam, Germany. Download PDF (416K) 2. Mahdi Jelodari Mamaghani, Jim Garside, "High-level Synthesis of GALS Systems," Workshop on Designing with Uncertainty - Opportunities and Challenges (PAnDA), March 2014, York ,UK. Download PDF (115K) 1. Mahdi Jelodari Mamaghani, Will Toms, Jim Garside, "eTeak: A Data-Driven Synchronous Elastic Synthesiser," Intl. Conference on Application of Concurrency to System Design (ACSD), July 2013, Barcelona, Spain. Download PDF (130K)

News & Updates

Balsa Language (balangs) for High-level Synthesis initiated on github! https://github.com/balangs We're looking forward to provide a FPGA backend for the go-like langauge of Balsa. This project borrows eTeak comipler for synchronous synthesis of large scale systems enclosed in a large elastic ecosystem.

Updated on 29th October 2015Back from the UK ICT Final event. Happy for Leo Laughlin from BristolU who won this year's prize in Technology Everywhere category.

Updated on 15th September 2015An entry for the 2nd Round of UK ICT Pioneers 2015:

Started to collaborate with the DSD Lab of the University of Tehran under Dr Siamak Mohammadi.

Software Release: please check out Software section on top to gain access to eTeak.

A Demo of the De-Elastisation technique, presented @ DATE 2015:

This video shows a part of my demo at DATE 2015 conference. The differences between the asynchronous (Elastic) and synchronous (De-Elastic) version of a dataflow circuit in terms of area, performance and power are demonstrated. We leverage Teak's visualisation engine to explicitly show the switching activities within dataflow circuits.A Demo of eTeak, presented @ ASYNC 2014:

The page initiated.